اليوم ، تعلن EdgeQ بدء تشغيل الهاتف الخلوي 5G عن إضافة عضوين جديدين إلى مجلسها الإستشاري - الرئيس التنفيذي السابق لشركة Qualcomm بول جاكوبس ، ومدير التكنولوجيا التنفيذي السابق لشركة Qualcomm Matt Grob. وتتمثل مهمتهم في خفض التكلفة الإجمالية للملكية (TCO) لمحطات القاعدة الخلوية 5G إلى النصف عن طريق الإستفادة من تصميمات RISC-V للأجهزة وتوسيعها.

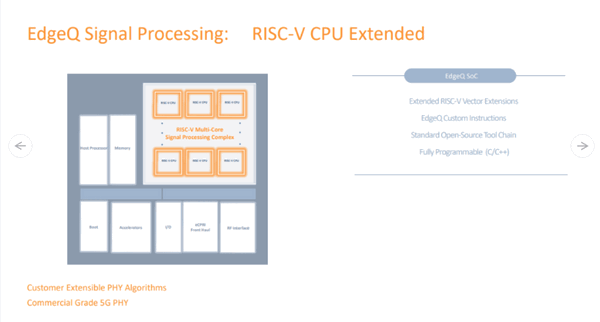

تقليدياً ، تميل أجهزة شبكة الوصول اللاسلكي (RAN) إلى أن تكون ذات تصميم مغلق وذات ملكية عميقة - مثلها مثل شبكة Wi-Fi الإستهلاكية وأجهزة الشبكة ، فهي تعتمد على ASICs ذات التصميم المغلق مع برامج التشغيل والبرامج الثابتة التي يوفرها البائع. بشكل عام ، لا يمكن ترقية هذه الحزم المغلقة لإستيعاب البروتوكولات الجديدة وحالات الإستخدام - على سبيل المثال ، يجب إستبدال وحدة الراديو أو الوحدة الموزعة المصممة لشبكات الجيل الرابع بالكامل من أجل خدمة أجهزة 5G.

على النقيض من ذلك ، يمكن للبائعين تنفيذ حلول OpenRAN الخاصة بهم ، والتي تنفذ بشكل عام وظائف أقل في الأجهزة ، وأكثر في البرامج التي تعمل على أنظمة التشغيل التقليدية مثل Linux. لكن تنفيذ مثل هذا O-RAN بشكل صحيح يتطلب خبرة بروتوكول عميقة جداً للحصول على الحق ، وتميل إلى أن تكون متعطشة للغاية للطاقة وصيانتها بمجرد الإنتهاء.

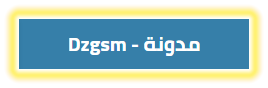

يتمثل نهج EdgeQ في تقسيم الإختلاف بشكل فعال بين طرق السيليكون المغلقة التقليدية و O-RAN باهظة الثمن. رخصت شركة EdgeQ تصميمًا مرجعياً لوحدة المعالجة المركزية RISC-V وأضافت تعليمات جديدة للأجهزة لتسريع عمليات الرياضيات المتجهية باهظة الثمن من الناحية الحسابية اللازمة للتعامل مع اتصالات 4G و 5G ومعالجة الإشارات.

يقول Adil Kidwai ، نائب الرئيس ورئيس إدارة المنتجات في EdgeQ ، إن التعليمات الجديدة ليست الإمتداد القياسي لمتجه RVV الرياضي. يصف Kidwai إمتداد ISA الخاص بـ EdgeQ على أنه مجموعة من "التعليمات الموجهة المخصصة لتحقيق أداء عالٍ باستهلاك منخفض للطاقة لحلول البنية التحتية لشبكات الجيل الخامس."

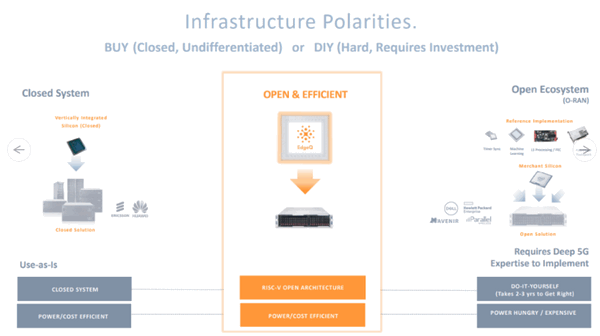

وفقاً للرئيس التنفيذي لشركة EdgeQ فيناي رافوري ، فإن النهج المبتكر للشركة يخفض إستهلاك الطاقة من 100 واط (باستخدام حل يعتمد على Xeon) إلى 10 واط ، مع إنجاز جميع الأعمال تقريباً في شركة EdgeQ's SoC نفسها. في DU في الأبراج الخلوية ، يمكن أن يعني ذلك تكثيف الأجهزة المنفصلة لتسريع التعلم الآلي ، ومزامنة المؤقت ، وتسريع FEC ، والنقل الأمامي والوسطي ، ومعالجة L1 كلها إلى أسفل EdgeQ SoC الفردي - ومرة أخرى وفقاً لـ EdgeQ ، قم بقطع إجمالي تكلفة الملكية بمقدار تصل إلى 50 بالمائة.

نظراً لأن تعليمات الرياضيات الموجهة اللازمة لمعالجة إشارات 5G والإتصال هي إلى حد كبير هي نفسها المطلوبة لمهام التعلم الآلي ، يمكن تخصيص سعة المعالجة الزائدة في وحدة المعالجة المركزية في EdgeQ لمعالجة ML المحلية. وفقاً لرافوري ، يعد الإتصال الخلوي عبئاً سريعاً ، حيث تقضي وحدة المعالجة المركزية معظم وقتها في وضع الخمول. يمكن تقسيم أنوية RISC-V CPU بشكل مباشر ، مع تخصيص بعضها لـ 4G / 5G وبعضها لـ ML ، أو يمكن توزيع أعباء العمل على أساس جودة الخدمة (QoS) المدارة.

نعتقد أن أهم جزء في تصميم EdgeQ هو مرونته. من خلال تزويد العملاء بإمكانية الوصول الحقيقي لـ C / C .. إلى RISC-V SoC ، لا تتيح EdgeQ الإبتكارات فحسب ، بل القدرة على التكيف في المستقبل. يمكن تحديث مثل هذا النظام في مكانه لإستيعاب ترقيات البروتوكول المستقبلية ، حيث تحتاج الأنظمة الأقل مرونة إلى "ترقية رافعة شوكية" - مما يعني رفع النظام القديم لأعلى ، والإنزلاق في النظام الجديد ، ثم نقل النظام القديم إلى إعادة التدوير .

ليست الشركة الوحيدة في هذا المجال العام - بدأ كل من بائعي محركات الأقراص الثابتة Western Digital و Seagate في تنفيذ تصميمات RISC-V في بعض تصميمات الأجهزة القادمة ، وقد قاموا بذلك لأسباب مماثلة. نأمل أن نرى إستمرار هذا التوسع في تصميماتها في مساحات السيليكون المغلقة سابقاً.

هذا رسم تخطيطي للوحة مضيفة. توجد وحدة المركزية المركزية RISC-V الموسعة من EdgeQ في الجزء العلوي الأيمن ، "Host Processor" على اليسار هي وحدة المركزية التي تعمل عليها نظام التشغيل Linux بالفعل.

"المتكامل الحرف رأسياً" هو نوع التصميم الذي تراه في الهاتف الذكي: الصندوق الأسود ، ومودم ASIC

تتعامل مع إمتدادات Vector-math ISA على تجميعها معالجة واحدة بأداء مهام متعددة مستويات كفاءة ASIC - التعامل مع البرامج الثابتة التي يمكن تحديثها بسهولة.